### Improving Fault Attacks On Embedded Software Using RISC Pipeline Characterization

<u>Bilgiday Yuce</u>, Nahid Farhady Ghalaty, Patrick Schaumont Virginia Tech

#### FDTC 2015

This research was supported through NSF Grant 1441710, Grant 1115839, and through SRC.

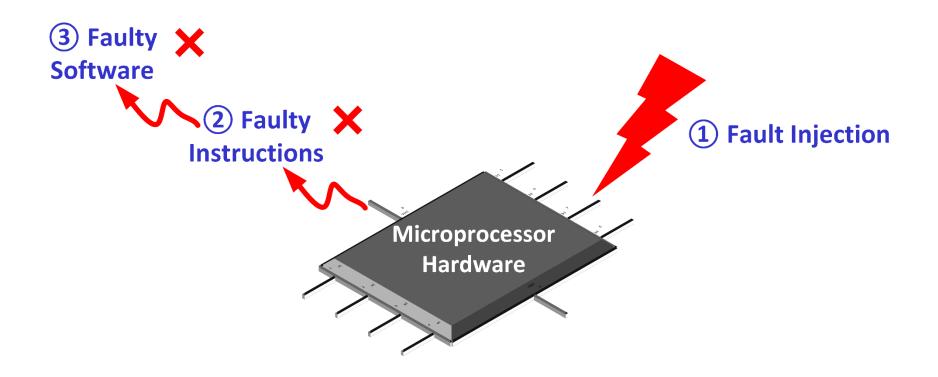

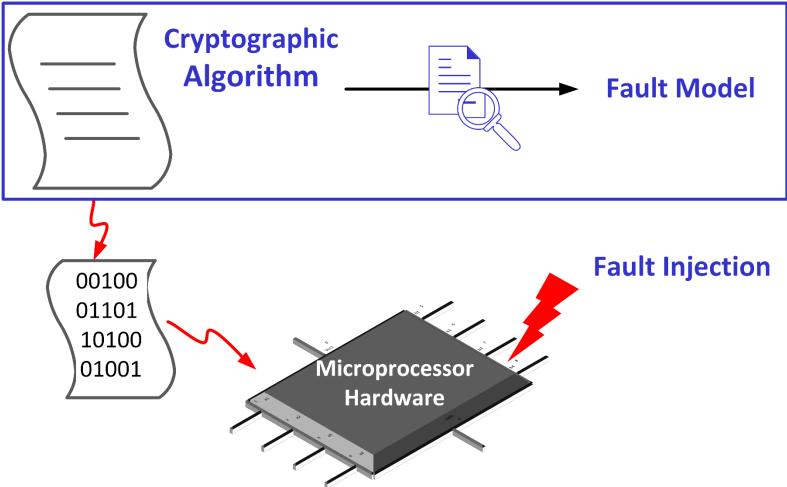

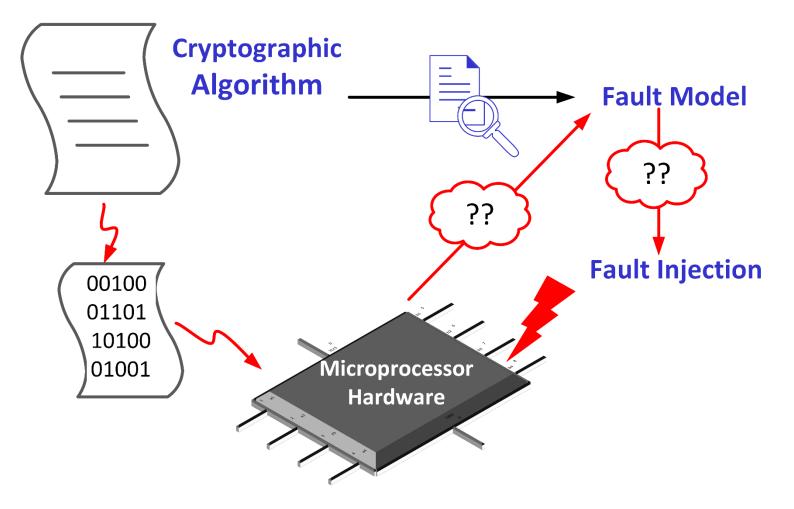

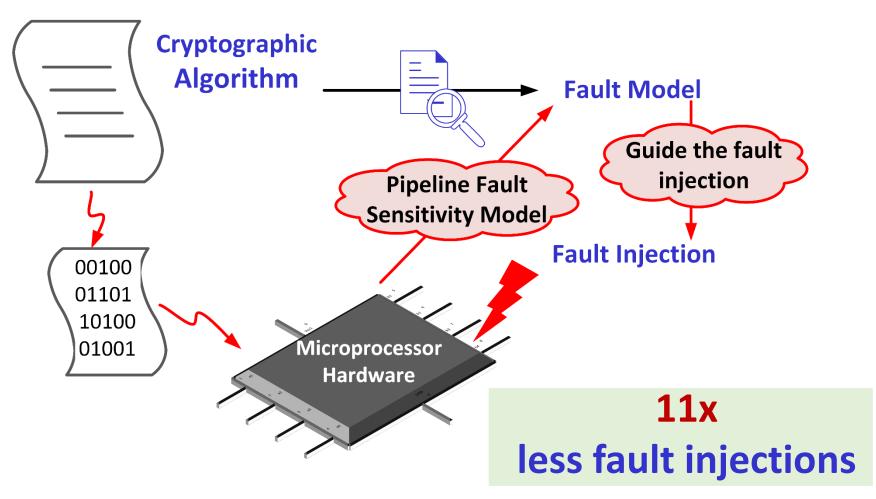

• Hardware determines the fault behavior of software.

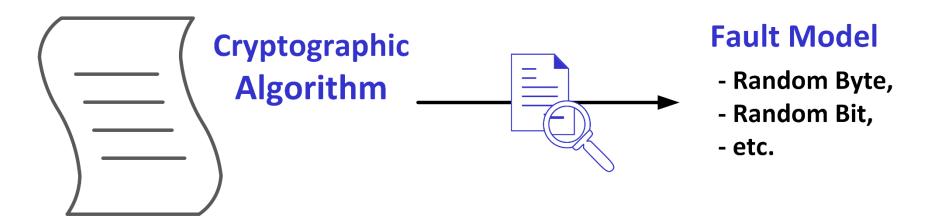

• Start with a high-level assumption on fault behavior

- Virginia Tech. Traditional Methods (2)

- There is a gap between assumptions and reality.

# Virginia Tech. Problems of the Traditional Methods

• Microprocessor hardware is not fully utilized.

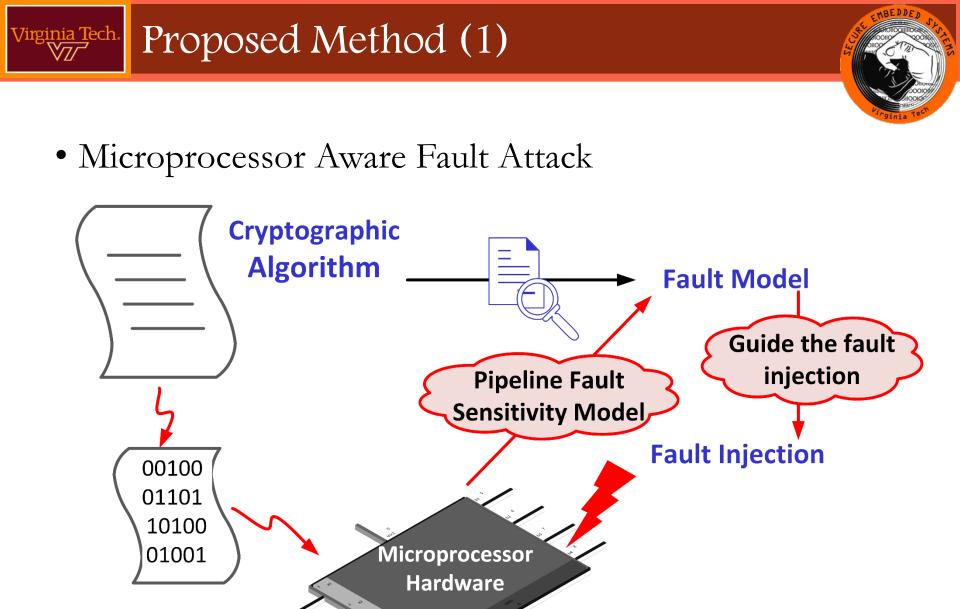

• More practical fault models and efficient injection

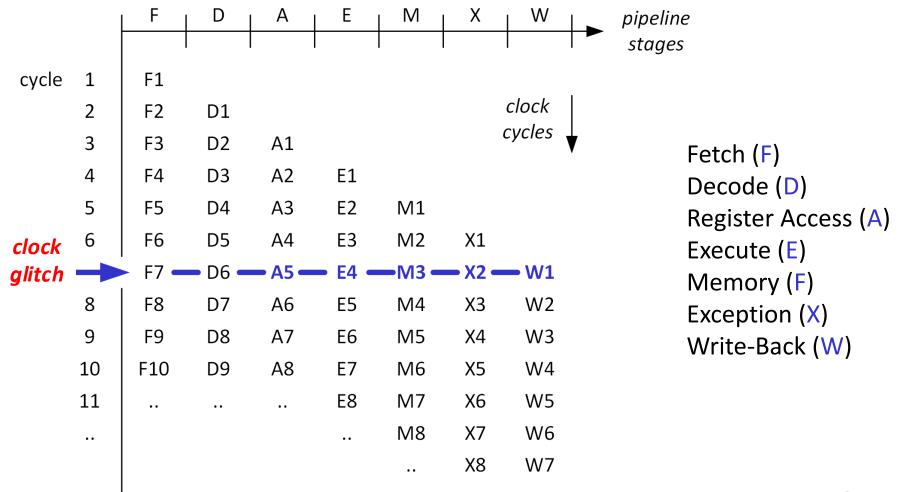

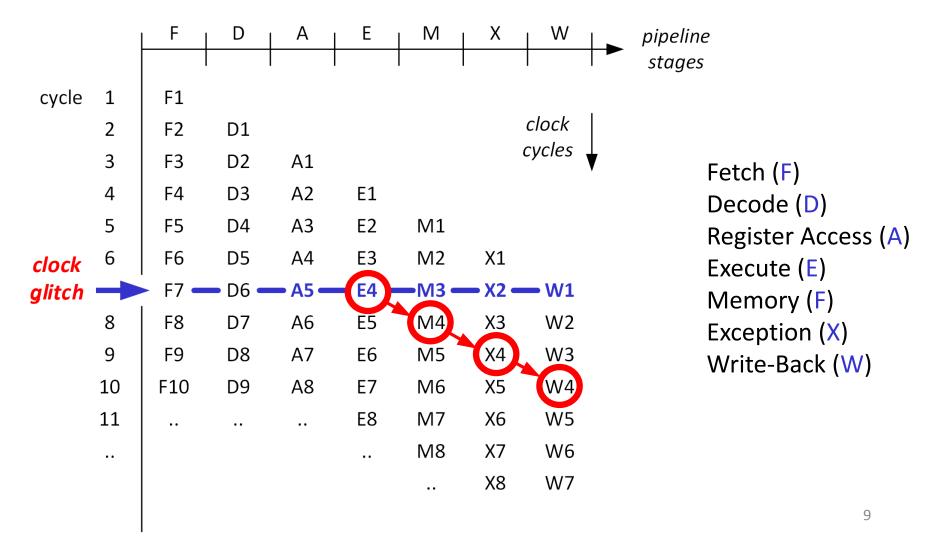

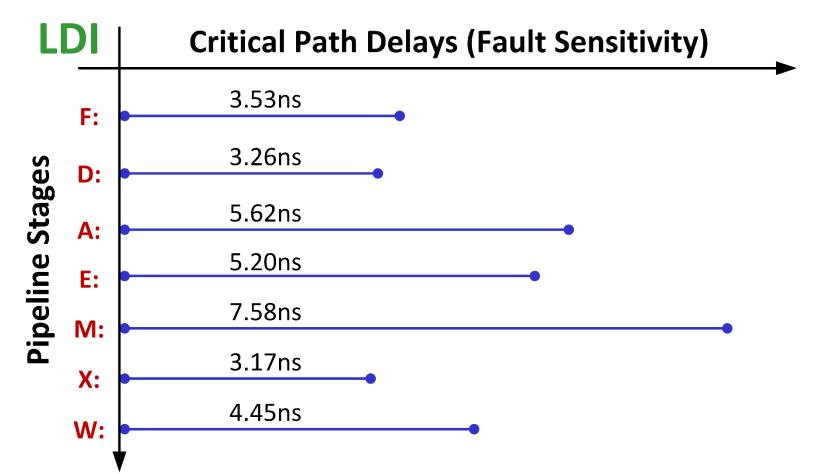

### • 7-Stage RISC Pipeline:

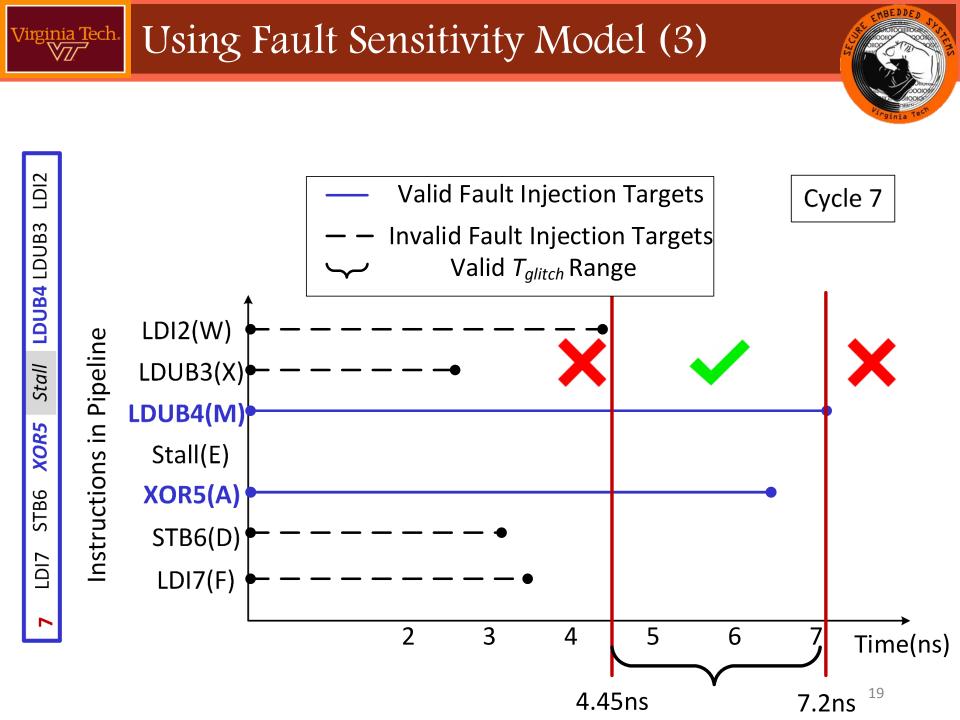

• If E4 has the highest critical path (i.e, fault sensitivity):

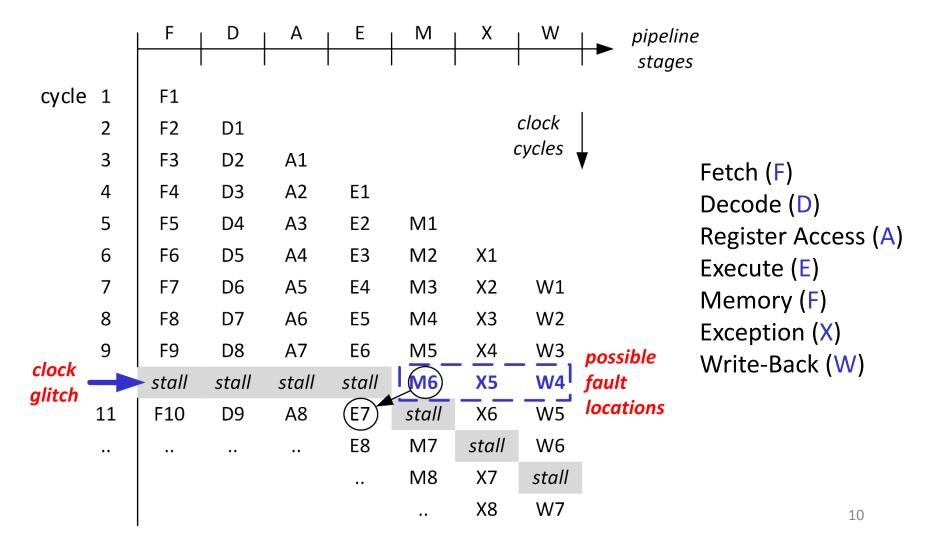

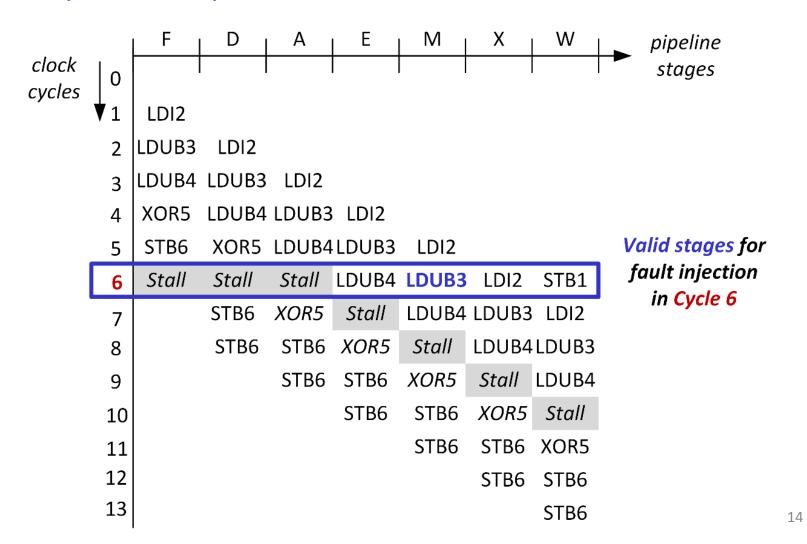

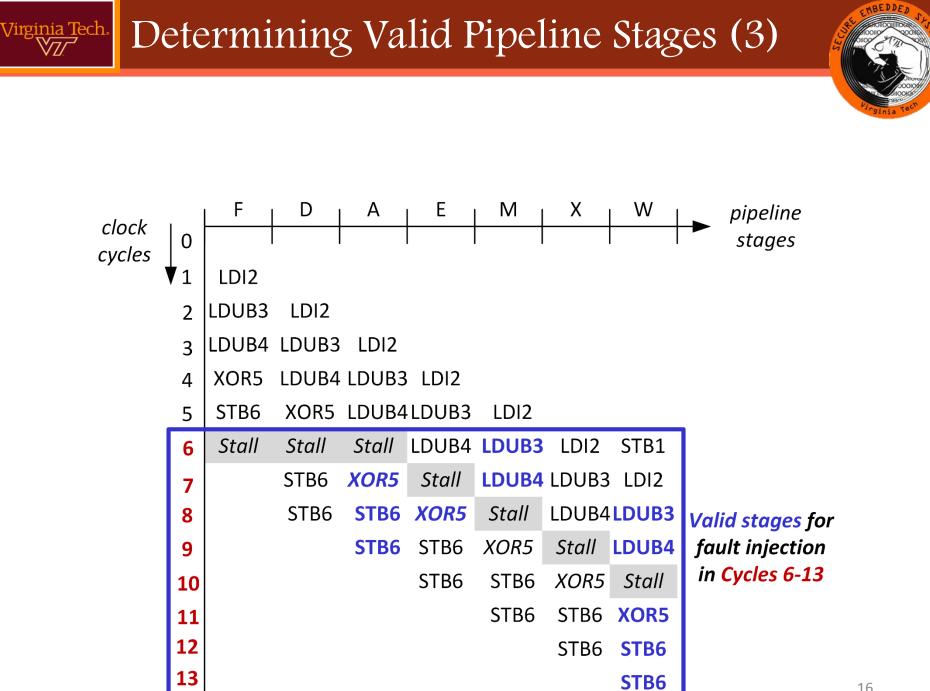

• Pipeline stalls blind the stalled stages from glitches.

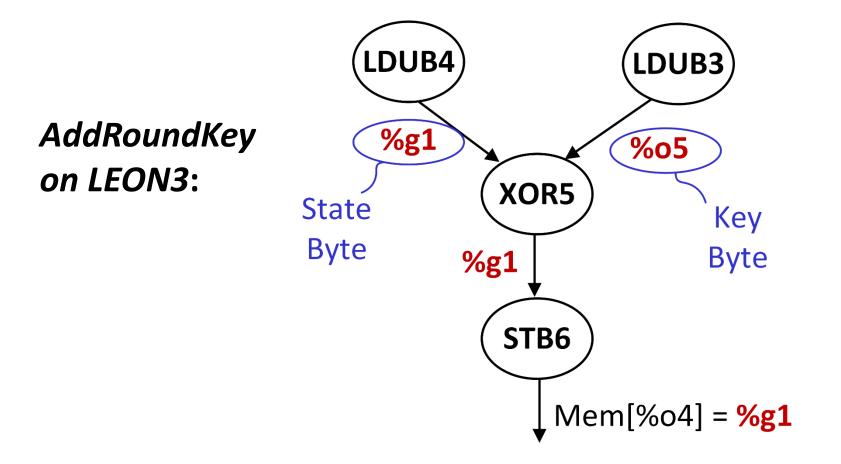

- Case Study:

- Fault Analysis: Differential Fault Intensity Analysis (DFIA)

- Software: AES

- Hardware: LEON3 Processor

- DFIA [Ghalaty et. al, FDTC'14]:

- Relies on a biased fault behavior

- Gradual fault behavior in proportion to the fault intensity

- EthBEDDED Starting Control Con

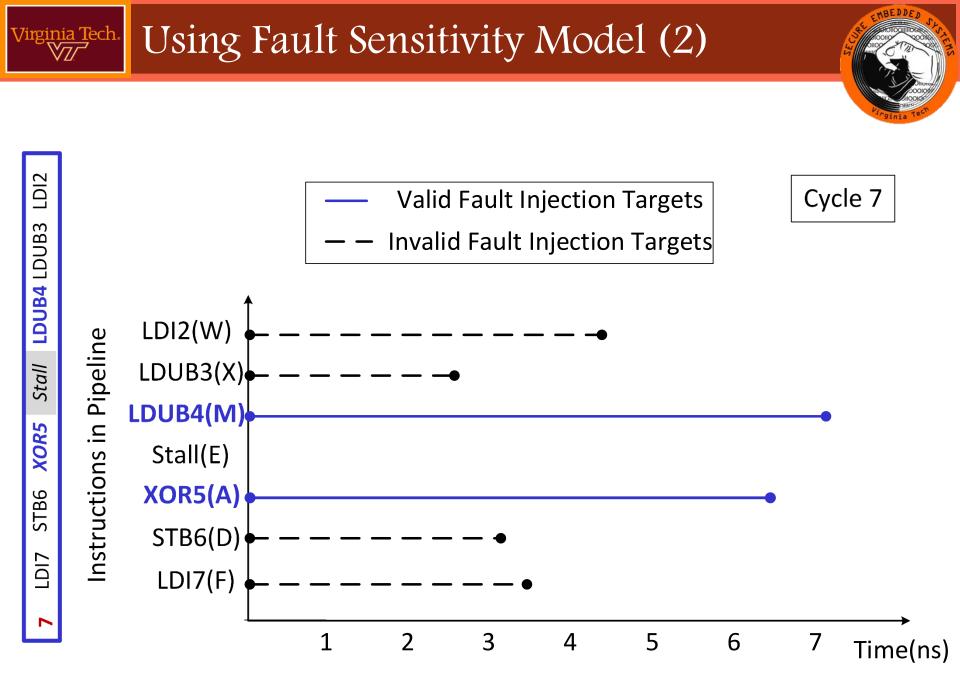

- Fault sensitivity of each (instruction, pipeline stage)

## Virginia Tech. Determining Target Instructions

#### • Objective:

• Biased faults in the AddRoundKey at AES Round 9

• Analyze each cycle of execution

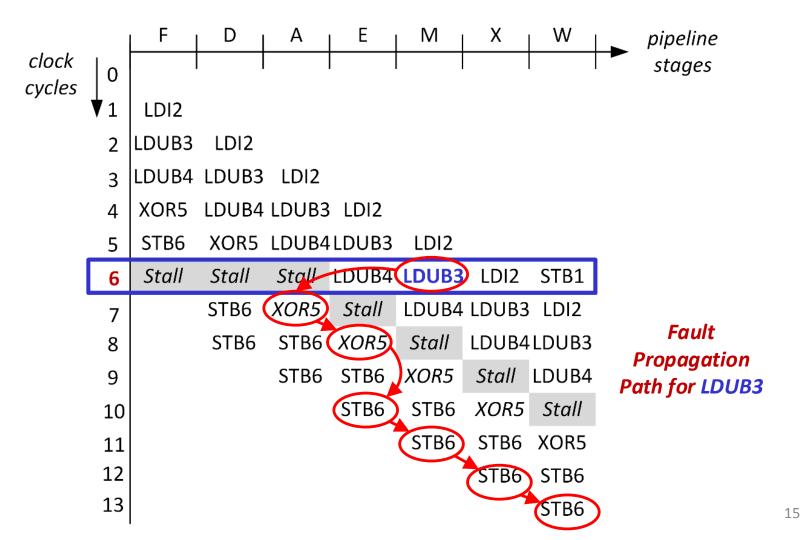

• Propagation of a biased fault injected into (LDUB3, M)

Instructions in Pipeline

LDI2(W) LDUB3(X) LDUB4(M) Stall(E) XOR5(A) STB6(D) LDI7(F)

Virginia Tech. Using Fault Sensitivity Model (1)

Cycle 7

- Fault Injection Experiments on a LEON3:

- Implemented on a SPARTAN-6 FPGA

- Clock glitch injection

- A DFIA attack on a AES software program:

- 1 secret key and 1 plaintext

### • Our approach requires ~11x less fault injections.

|                     | Total # of<br>Attacked Cycles | Total # of<br>Fault Injections |

|---------------------|-------------------------------|--------------------------------|

| Traditional Methods | 13                            | 1040                           |

| Our Method          | 6                             | 90                             |

|                     |                               |                                |

|                     |                               | ~ 11x                          |

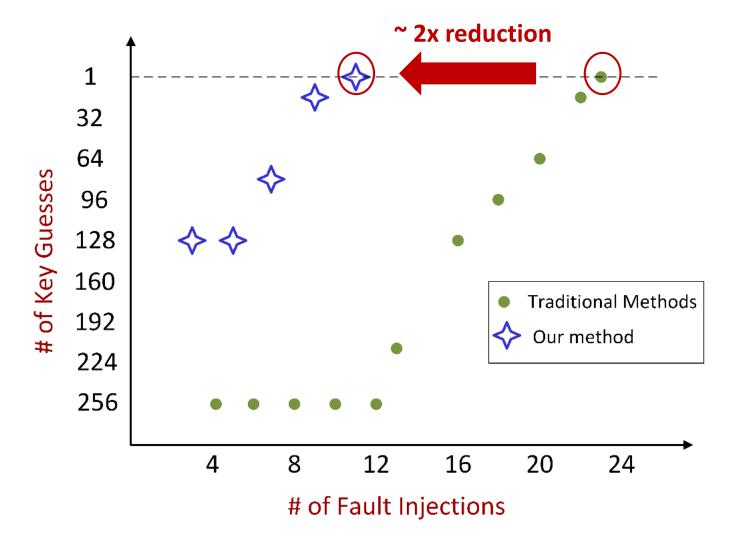

• DFIA retrieves the key byte quicker with our method.

Virginia Tech.

Results (3)

- For efficient fault attacks on embedded software, use

- micro-architectural properties (i.e. fault sensitivity model)

- architectural properties (i.e. pipeline analysis of the software)

- With a microprocessor aware fault attack method:

- Possible to tune the injected faults in the software

- ~11x less fault injections

- Traditional methods need a revision